GPIO_PinAFConfig ( GPIOD, GPIO_PinSource10, GPIO_AF_FSMC ) // D15 GPIO_PinAFConfig ( GPIOD, GPIO_PinSource9, GPIO_AF_FSMC ) // D14 // GPIO-PortD Pin9 will used as FSMC This example do a part of the FSMC Setup by using a structure to map the FSMC lines. Every Screw thats required to be turn should be self described by a regular name. A good example that demonstrate what i mean is the FSMC init Structure that Needs to be filled with valid Parameters. You must beware about the huge amount of available Registers and their names. The next Point, same reason is the use of the CMSIS-Library and Std-Library instead Manipulation the bits directy. For a beginner in Cortex-M programming, the homogene IDE like µVision from Keil make the start easier. To get the IDE works with the JTAG and the Environment Setup is done, a couple of hours could be passed. At first, i wondering why the GCC Compiler is prefered to use in combination of the worst IDE like "Eclipse" and their commons. I would like to add some lines to the FSMC and Display connectivity. But I still have pixels in random places or I haven't in other (for example ragged diagonal line or multicolored lines on right side on third image ). Please don't look at the colors, I have fixed them (RGB to BGR).

#define SCREEN_PCLK (SCREEN_HSYNC_PERIOD * SCREEN_VSYNC_PERIOD * SCREEN_FPS) #define SCREEN_VSYNC_PERIOD (SCREEN_VSYNC_PULSE + SCREEN_VSYNC_BACK_PORCH + GDISP_SCREEN_HEIGHT + SCREEN_VSYNC_FRONT_PORCH) #define SCREEN_HSYNC_PERIOD (SCREEN_HSYNC_PULSE + SCREEN_HSYNC_BACK_PORCH + GDISP_SCREEN_WIDTH + SCREEN_HSYNC_FRONT_PORCH) => SCREEN_VSYNC_FRONT_PORCH = ( VT - VPS ) - GDISP_SCREEN_HEIGHT VT - VPS = GDISP_SCREEN_HEIGHT + SCREEN_VSYNC_FRONT_PORCH VPS = SCREEN_VSYNC_PULSE + SCREEN_VSYNC_BACK_PORCH => SCREEN_HSYNC_FRONT_PORCH = ( HT - HPS ) - GDISP_SCREEN_WIDTH HT - HPS = GDISP_SCREEN_WIDTH + SCREEN_HSYNC_FRONT_PORCH HPS = SCREEN_HSYNC_PULSE + SCREEN_HSYNC_BACK_PORCH VPS: non-display period in lines between the start of the frame and the first display data in number of linesįPS: vertical sync pulse (LFRAME) start location in lines. VT: Vertical Total period (display + non-display) VDP: Vertical Display period, normally height - 1 LPS: horizontal sync pulse (LLINE) start location in pixel clocks HPS: non-display period between the start of the horizontal sync (LLINE) signal and the first display data HT: Horizontal Total period (display + non-display) HDP: Horizontal Display Period, normally the width - 1 ** Display periods refer to pulses/timings that directly put pixels on the screen ** Non-display periods refer to pulses/timings that occur before or after the timings that actually put pixels on the screen

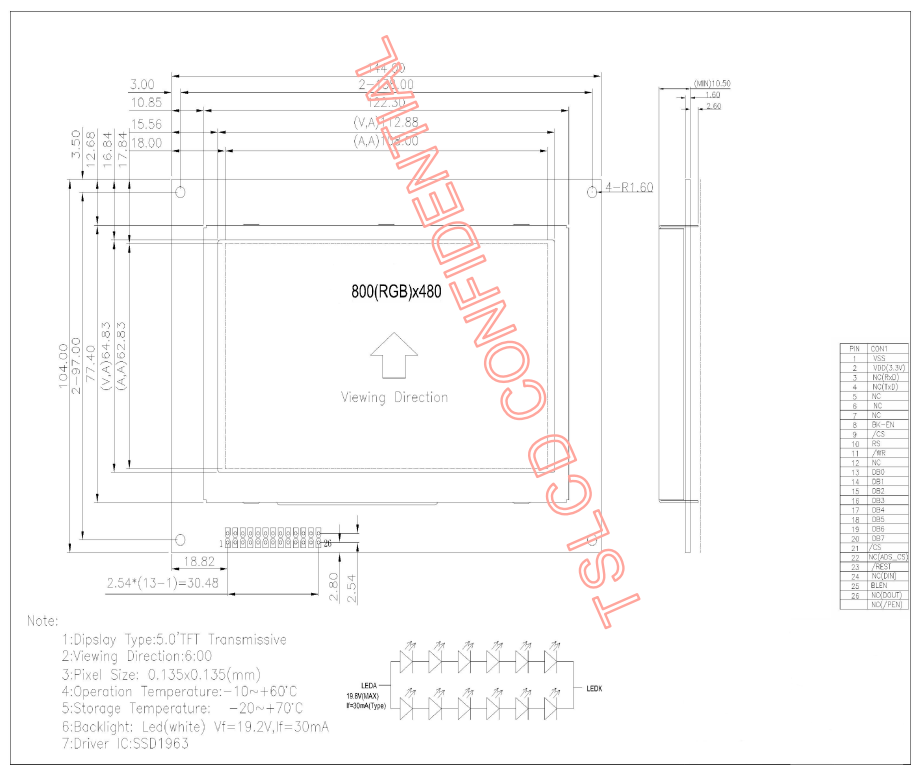

*** Datasheets normally use a specific set of timings and acronyms, their value refers to the number of pixel clocks * The timings need to follow the datasheet for your particular TFT/LCD screen (the actual screen, not the controller) * drivers/gdisp/SSD1963/gdisp_lld_panel_example.h

#Ssd1963 stm32 driver license#

* the license was not distributed with this file, you can obtain one at: * This file is subject to the terms of the GFX License.